TRENDS IN MEMS/MOEMS

NEXT - GENERATION OPTICAL MEMS/MOEMS TECHNOLOGIES AND DEVICES

WORKSHOP | NOVEMBER 15<sup>TH</sup>, 2017

# **PROGRAM**

# SOI FOR MEMS/MOEMS

## 13:00 SOI based platforms for next generation MEMS manufacturing

Vesa-Pekka Lempinen, Okmetic Oy, Finland

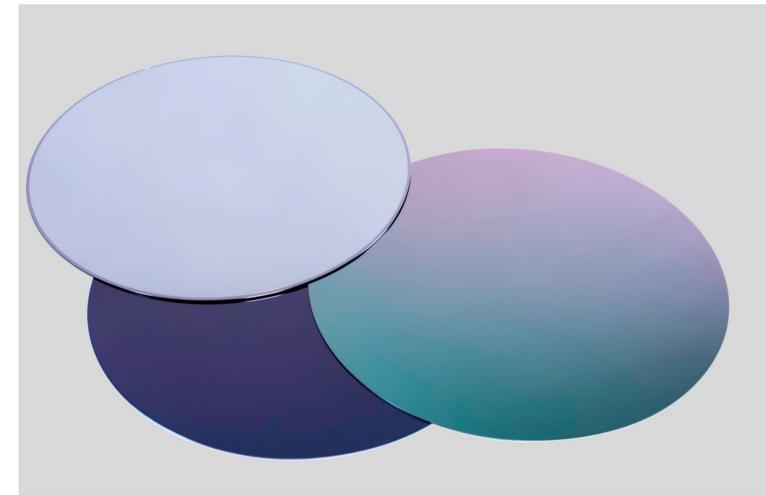

The rapidly growing IoT industry sets new demands for microelectromechanical system (MEMS) devices, the central building blocks of smart systems. Advanced MEMS devices are commonly built on thick-film bonded Silicon-On-Insulator wafers (BSOI), to gain benefits in precision and control of MEMS structures, device miniaturization and packaging.

Requirements for lower cost and higher volumes are driving towards sensor miniaturization, which requires higher precision BSOI starting materials to maintain existing level of device performance. Requirements for reliability and performance improvements on the other hand drive for improvements in precision of BSOI materials, and use of hermetically sealed structures enabled by Cavity SOI (C-SOI) wafers or wafer level packaging.

Okmetic solutions to these challenges are:

- Enhanced SOI (E-SOI) wafers, which are thick BSOI wafers with superior device layer thickness uniformity, independent of layer thickness

- C-SOI wafers, which enable part of sensor structures to be built into the SOI wafer as part of the wafer manufacturing process

- Through Silicon Vias (TSV) for sensor interconnections in wafer level packaging

- Combinations of above technologies

- During the presentations application examples of these wafer types will be shown and discussed...

#### MEMS/MOEMS SENSORS

### 13:40 Technological Application Fields for MEMS Sensors and Actuators

Luca Zanotti<sup>1</sup>, Alessandro Sanginario<sup>2</sup>

- <sup>1</sup> STMicroelectronics, Italy

- <sup>2</sup> Polytechnic of Turin, Italy

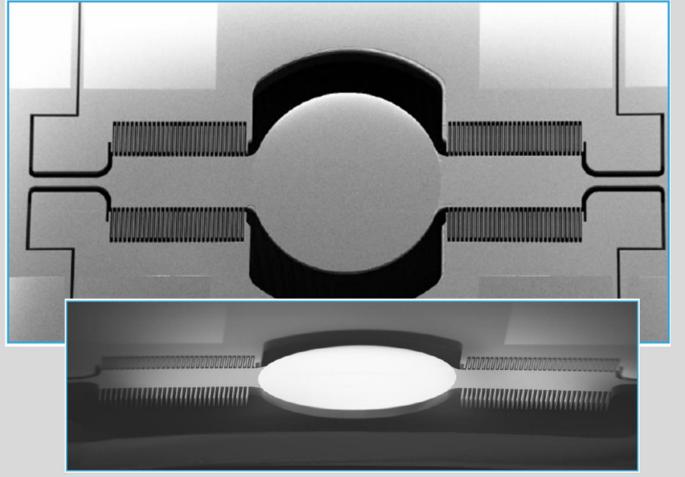

STMicroelectronics is among the European leading centers of excellence on "More Than Moore" technology identified by the High Level Group on KETs. MEMS developed technology capability generated during past years innovation and fueled a new generation of smart sensors and actuators quite often utilized in Consumer and Healthcare applications such as body area sensors and remote monitoring. Beyond the MEMS market for Inertial Measure Units (accelerometers, gyroscopes and magnetometers), Microactuators and micro-sensors have been integrated on silicon based on piezoelectric thin-films, for applications like in Data Storage, Ink Jet, Health Care, Automotive and Energy Scavenging, ultrasound transducers, gesture recognition, echography, micro-pumping, healthcare, etc. In particular way Earth magnetic field sensors are used in consumer applications such as GPS positioning, indoor navigation and in the omni-comprehensive mobile smart phones.

At the same time to maintain the pace advanced packaging technologies and vertical interconnections for full 3D integration have been developed with quite innovative solutions, included the through mold or Si Via and flip chips. Presentation will focus on a next-generation of MOEMS technologies and devices, global trends in the MOEMS fields, future applications, device processes, design, methodology and manufacturing.

#### PACKAGING, RELIABILITY

### 14:20 Design for manufacturability and reliability of metal bonding for wafer-level MEMS packaging

V. Vuorinen<sup>1</sup>, H. Viljanen<sup>2</sup>, G. Ross<sup>1</sup>, J. Dekker<sup>2</sup>,

- M. Paulasto-Kröckel<sup>1</sup>

- <sup>1</sup> Aalto University, Finland,

- <sup>2</sup> VTT Technical Research Centre of Finland, Finland

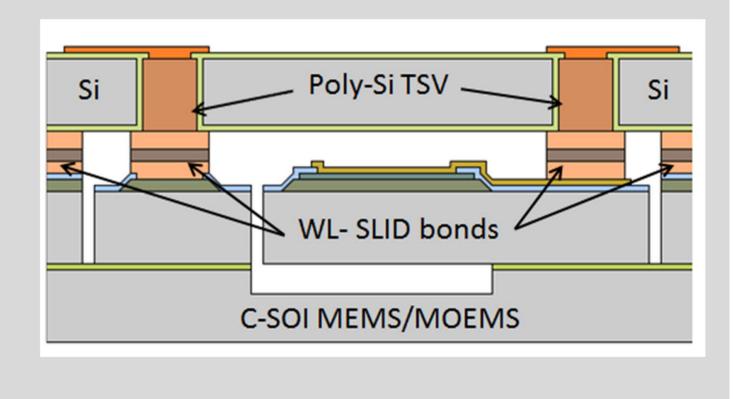

The basis for "More-than-Moore" approach in electronics 3D integration is provided by the development of bonding processes for different types of wafers and utilization of through-silicon vias (TSVs). Within the ENIAC Joint Undertaking Lab4MEMS-II project, the Finnish cluster (Aalto University, Okmetic Oyj, Murata Electronics and VTT Techinical Research Centre of Finland) is working on the design and manufacturing for reliable wafer level hermetic interconnection for MEMS/MOEMS devices. Process integration and reliability assessment for "vias before bonding" capping process has been carried out. Contact metallization structures, Poly-Si TSV manufacturing process flow, SLID bonding as well as cap wafer backside processes has been optimized. Different AuSn, CuSn and AlGe based metal bonding metallurgies and their compatibility to Cu, Ni and Pt contact metallization's were studied from manufacturability and reliability viewpoints with dummy wafers.